Z-80 Reimagined

I re-created the classic Zilog Z-80 microprocessor from the ground up, swapping its original 8080-compatible control logic for a streamlined, modern decode unit—while staying true to the Z-80’s 8-bit data bus, 16-bit address bus and register set.

Architecture Overview

8-Bit Registers

Six general-purpose 8-bit registers (B, C, D, E, H, L), plus A (accumulator),

F(flags) and their alternate set for context switches

16-Bit Registers

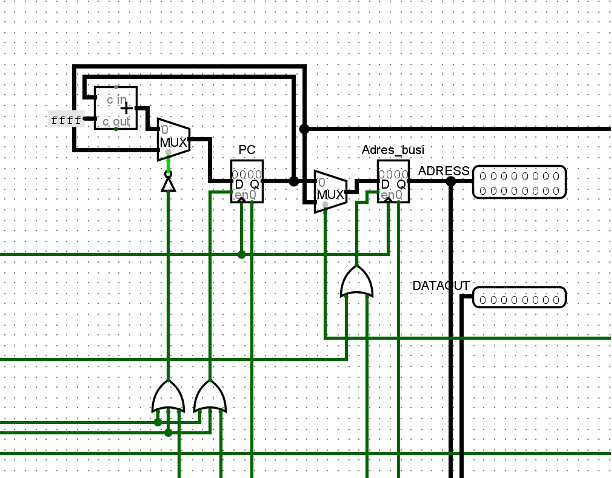

Program Counter (PC)

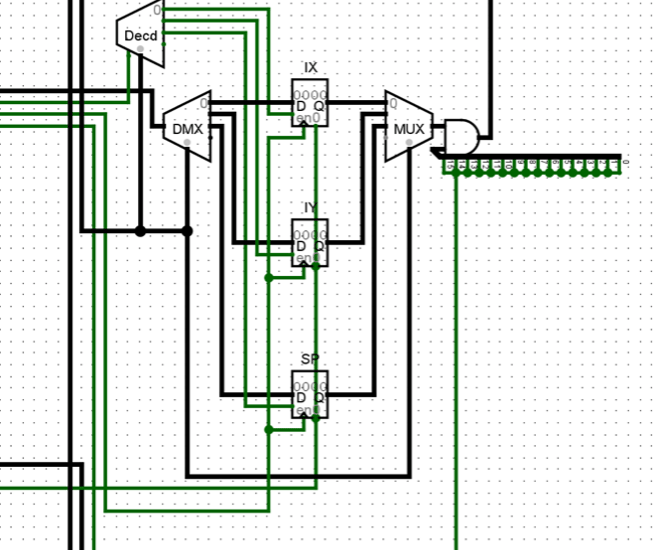

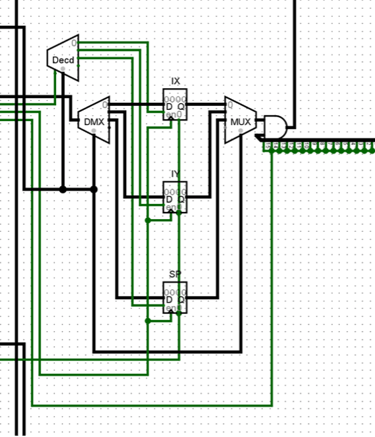

IX, IY and SP(Stack Pointer)

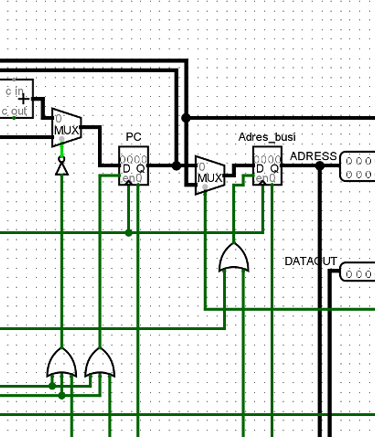

Program Counter (PC)

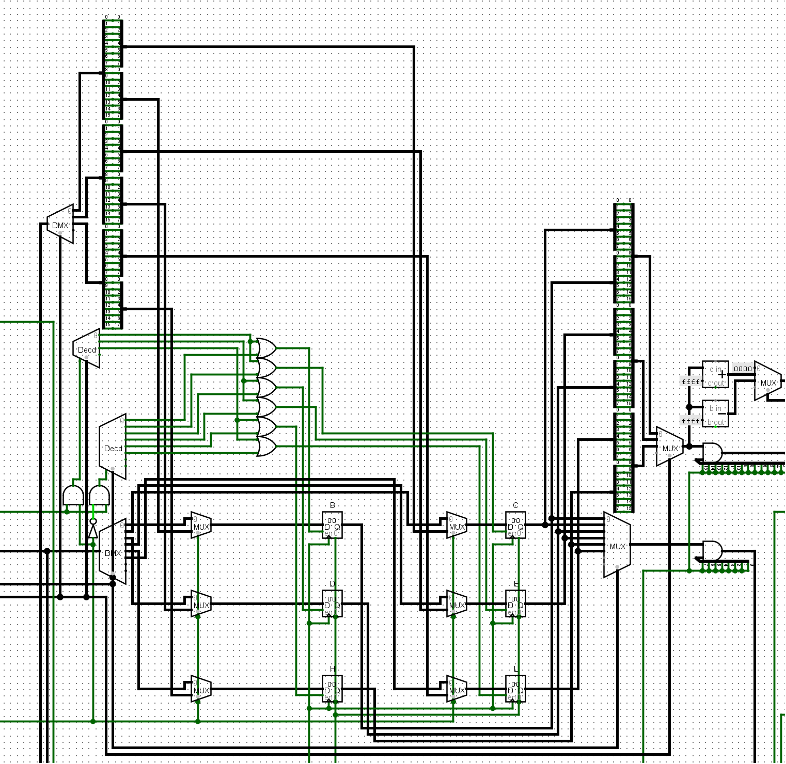

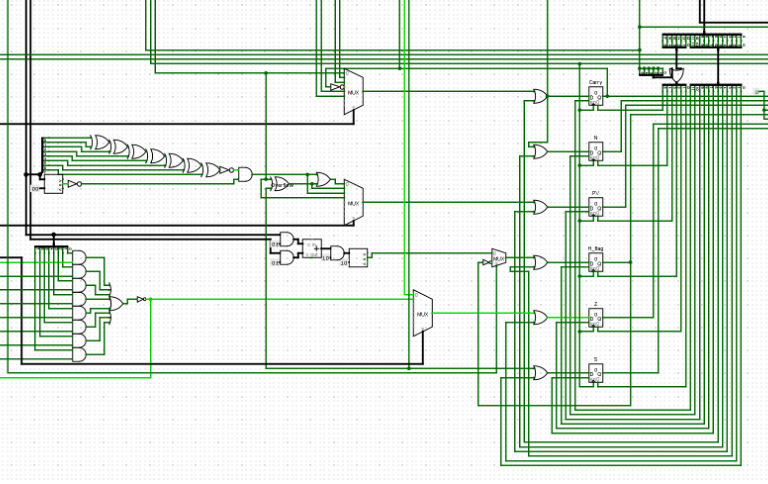

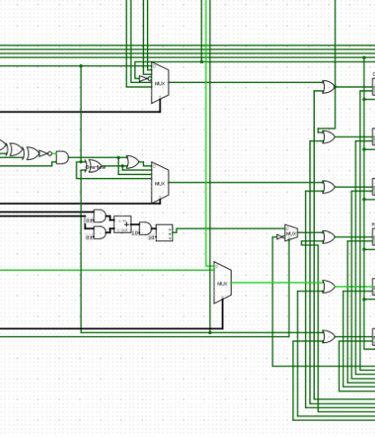

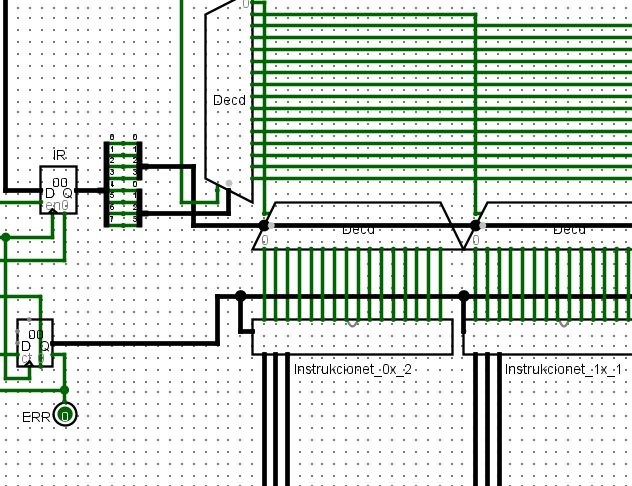

Control & Instruction Decode

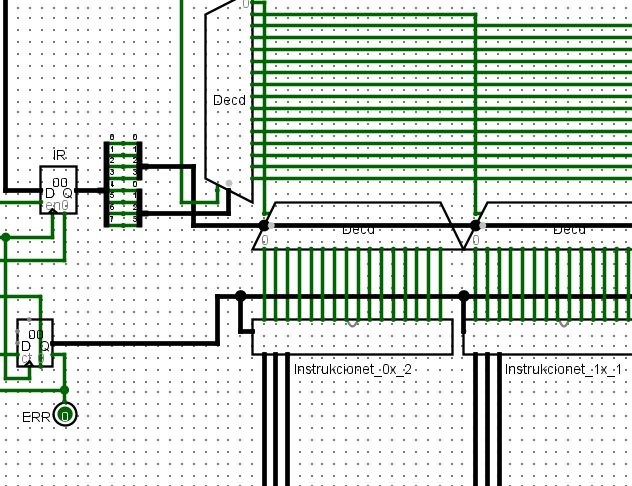

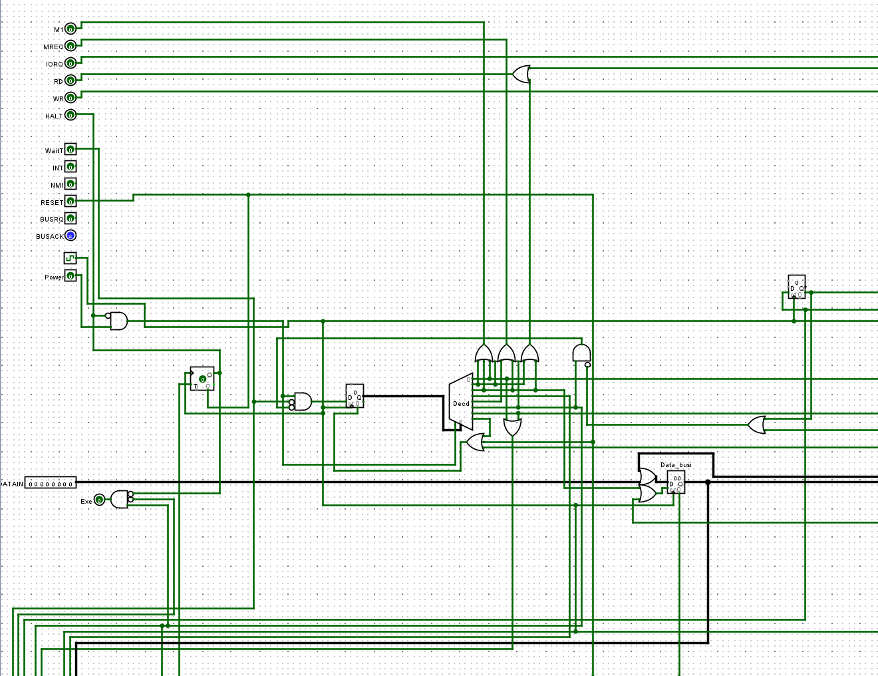

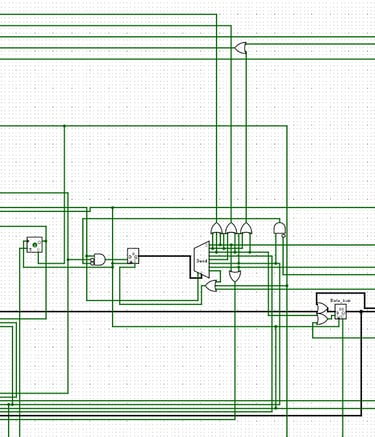

Data IN and Control part :

Control Logic and Instruction decoding system

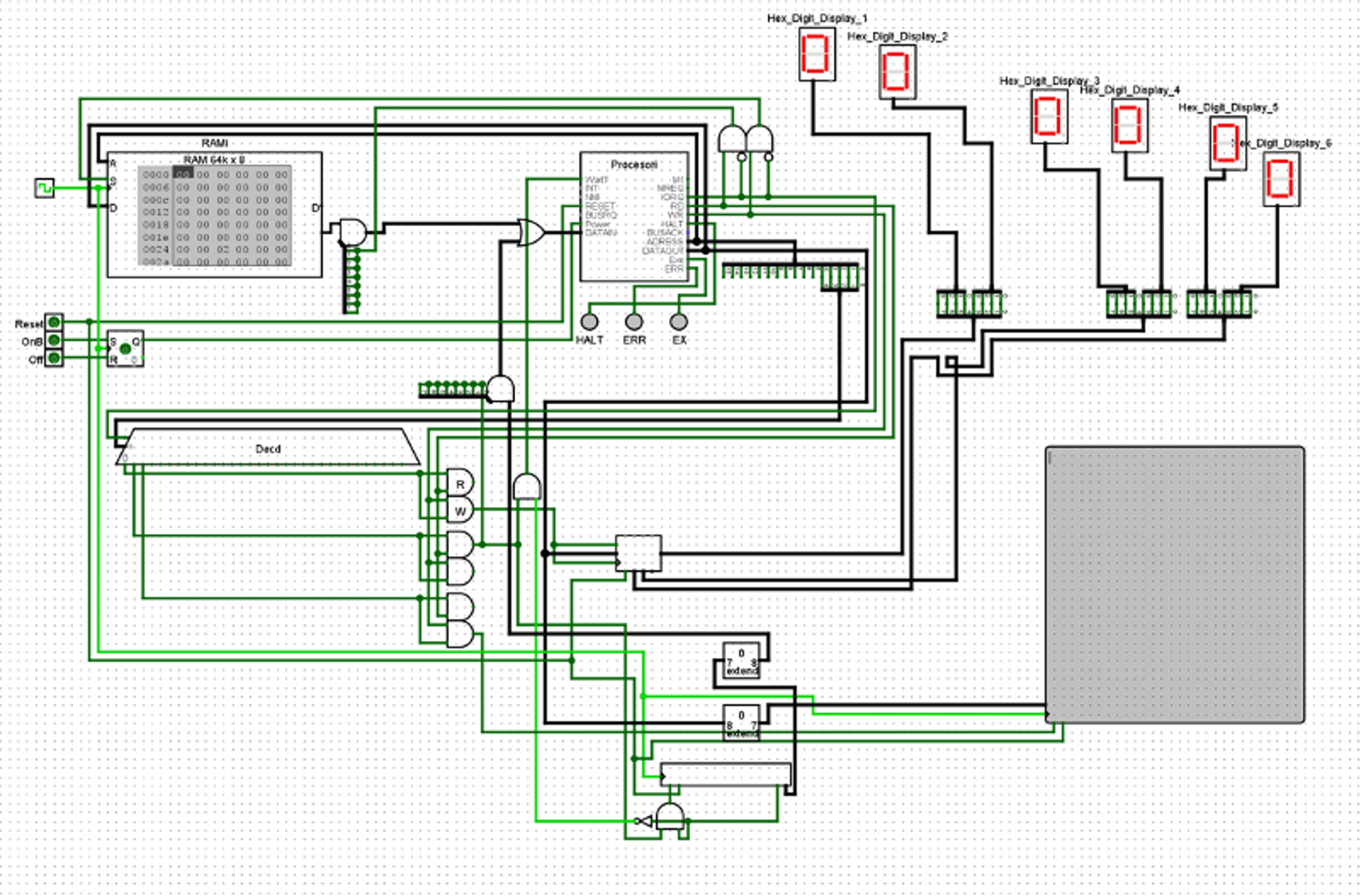

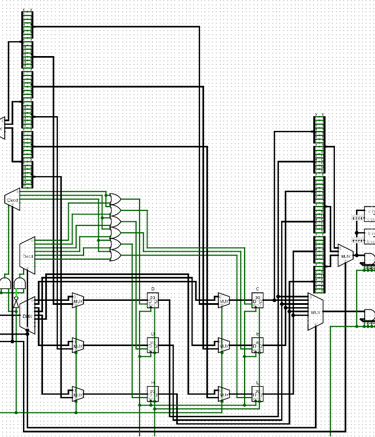

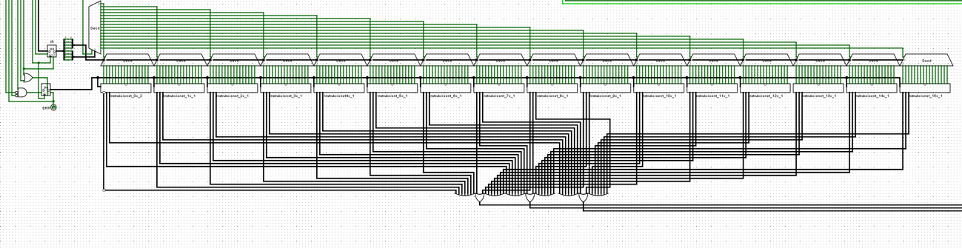

CPU

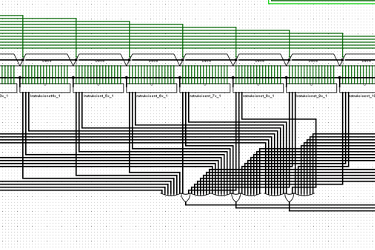

After combining all the parts, thought the project , including the Control logic and Instructions Decoding Systems the General Purpose Registers, Flag registers and all other parts here is the final CPU