8-Bit CPU

A complete 8-bit CPU built from the ground up in Logisim.

Simulated a full 8-bit datapath in Logisim, complete with:

• Ripple-carry ALU (add/subtract, AND/OR/XOR, logical shifts)

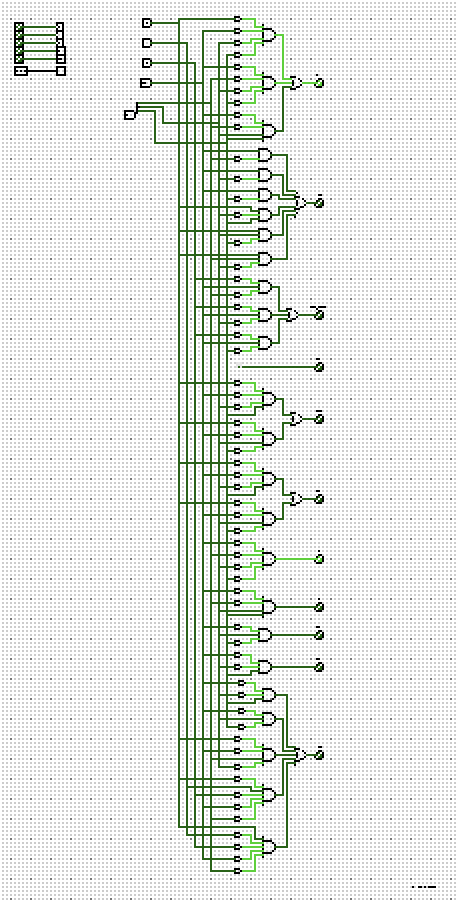

• Eight 8-bit registers (B, C, D, E, H, L, A, TEMP) + Flag register

• Program Counter (PC), Memory Address Register (MAR) & Instruction Register (IR)

• Custom control & decode logic for a 16-opcode instruction set

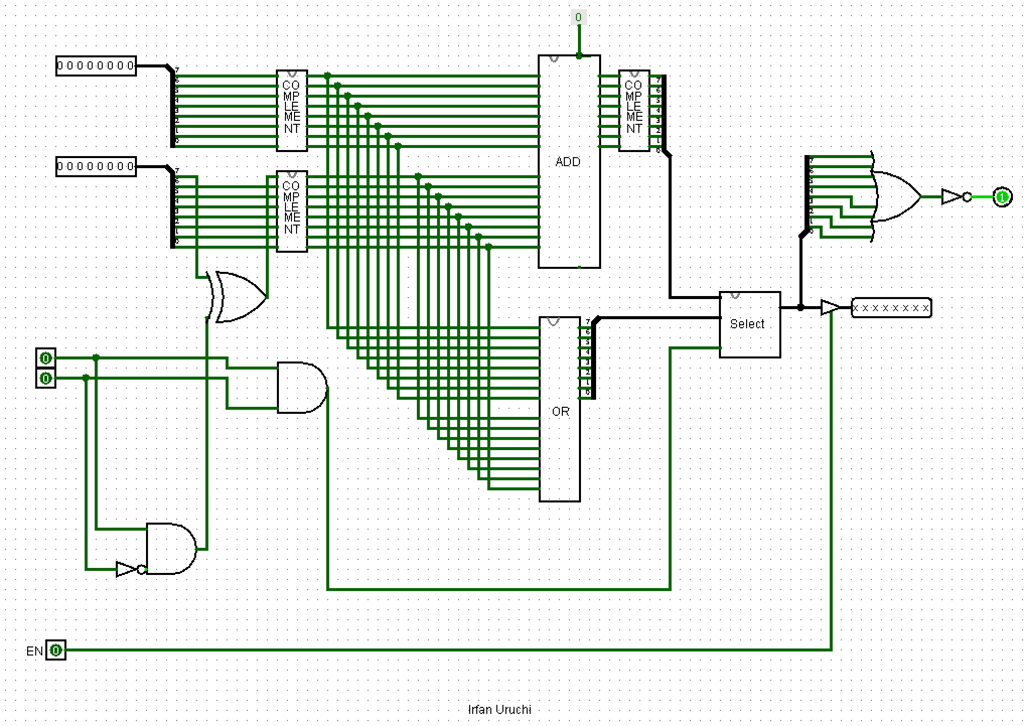

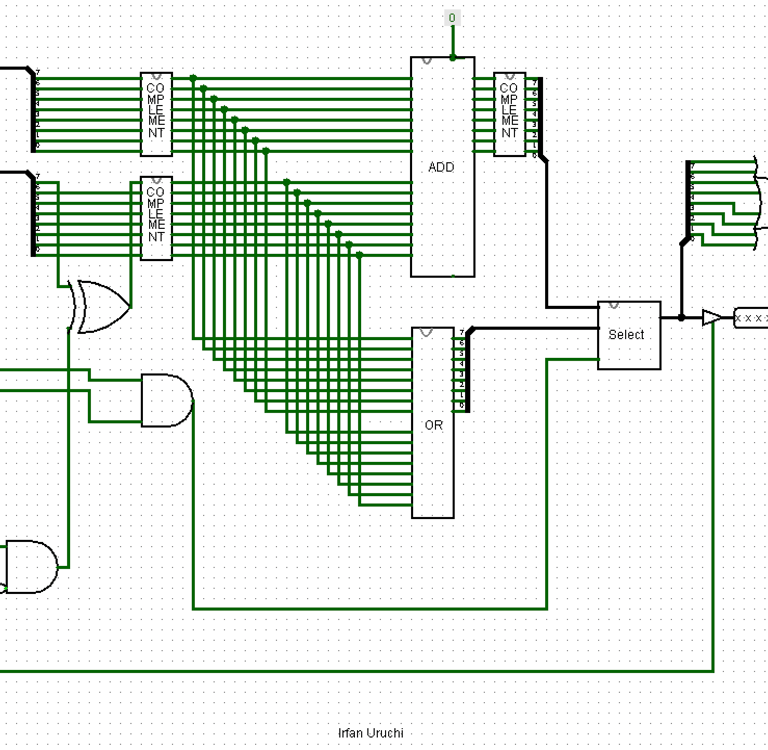

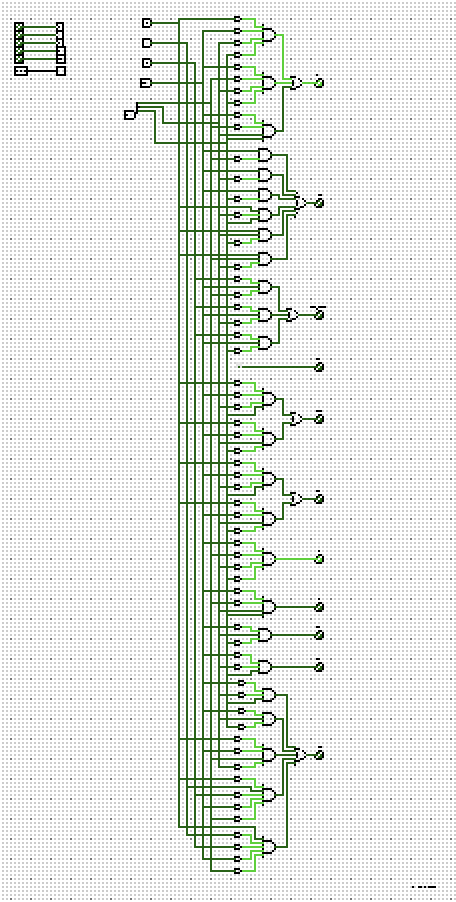

ALU

The ALU is the heart of the 8-bit CPU: I built it in Logisim by chaining together 4-bit full-adder modules for 8-bit add/subtract, then added AND, OR, and XOR gates for bitwise logic, plus a simple barrel shifter for left/right shifts and rotates. Its flag outputs (zero, carry, sign, half-carry) feed back into the control logic, letting the CPU make decisions based on every operation’s result.

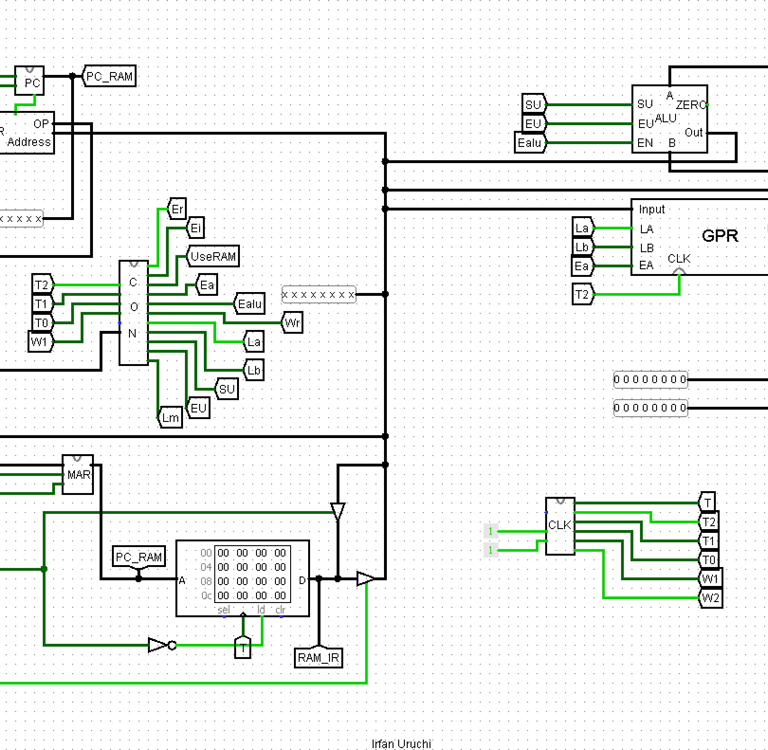

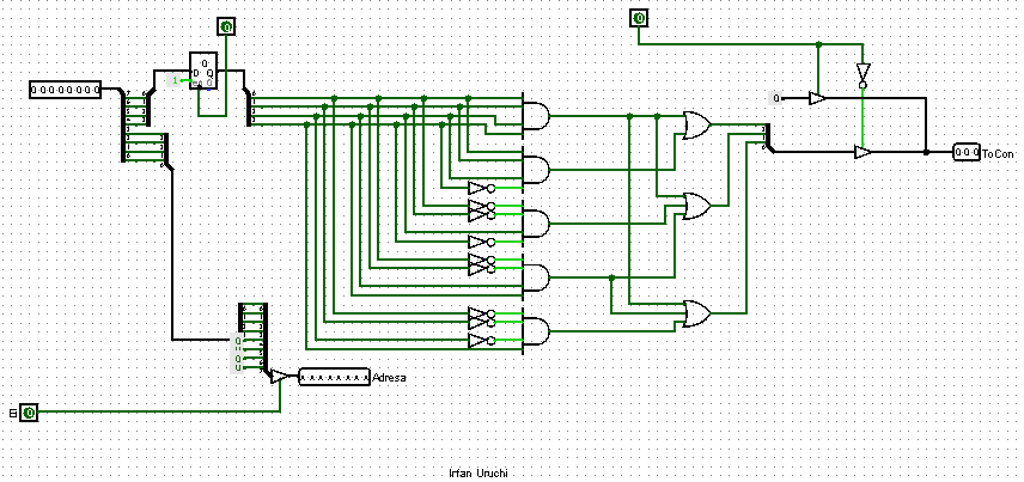

Program Counter & IR

The Program Counter (PC) auto-increments each cycle to fetch the next instruction into the Instruction Register (IR). From there, my custom decoder translates opcodes into control signals.

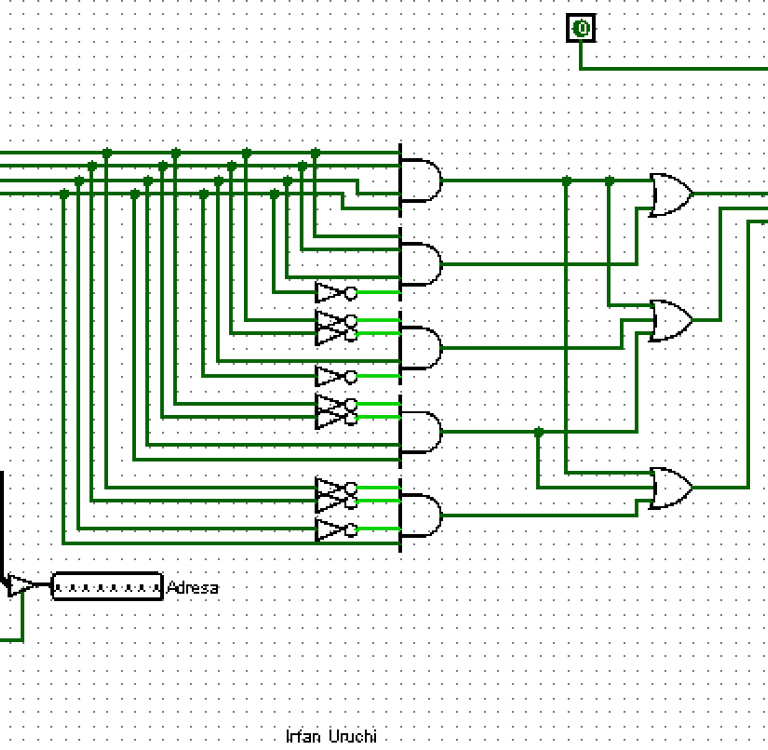

Control & Instruction Decode

A compact decode tree maps each 4-bit opcode to the correct control signals enabling register loads, ALU modes, and memory read/write strobes.

Implementation & Challenges

A compact decode tree maps each 4-bit opcode to the correct control signals enabling register loads, ALU modes, and memory read/write strobes.

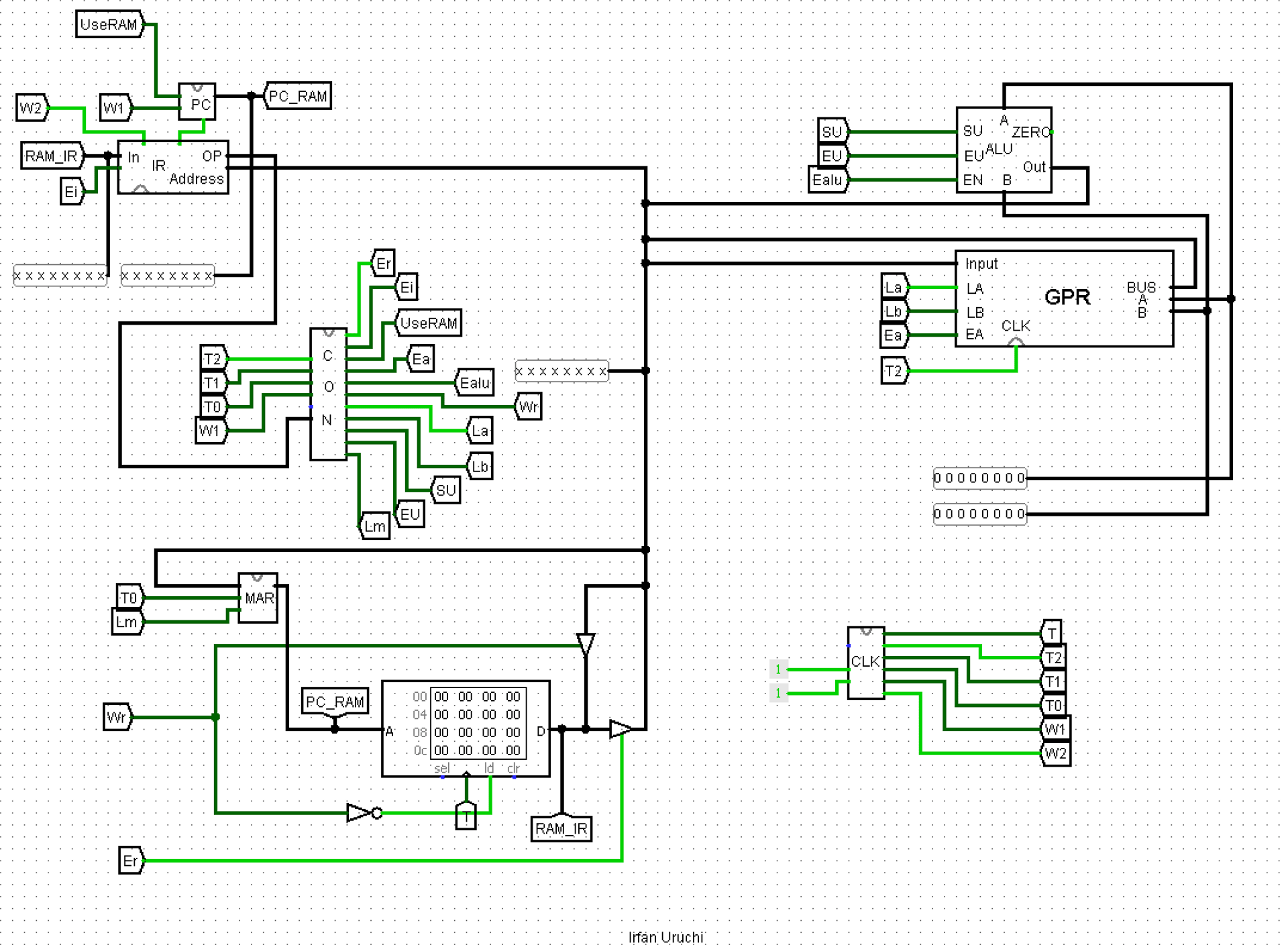

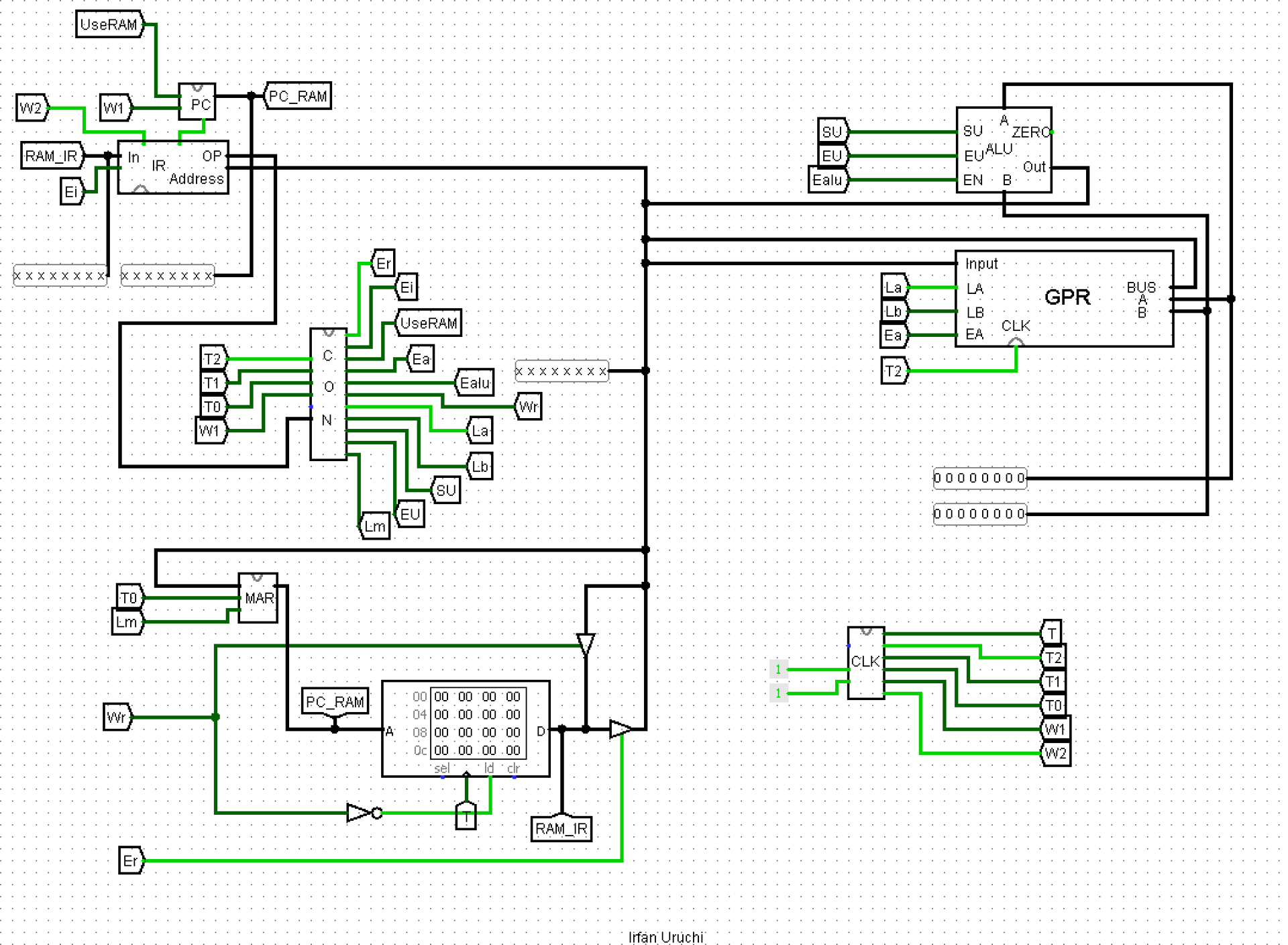

CPU Overview

Top-level Logisim view of the complete 8-bit CPU datapath